एंटी-अलियासिंग फिल्टर और वोल्टेज स्टेबलाइजर्स

स्मूथिंग फिल्टर को रेक्टिफाइड वोल्टेज रिपल को कम करने के लिए डिज़ाइन किया गया है। रिपल स्मूथिंग का मूल्यांकन स्मूथिंग फैक्टर q द्वारा किया जाता है।

स्मूथिंग फिल्टर को रेक्टिफाइड वोल्टेज रिपल को कम करने के लिए डिज़ाइन किया गया है। रिपल स्मूथिंग का मूल्यांकन स्मूथिंग फैक्टर q द्वारा किया जाता है।

चौरसाई फिल्टर के मुख्य तत्व कैपेसिटर हैं, कुचालक और ट्रांजिस्टर जिनका प्रतिरोध प्रत्यक्ष और प्रत्यावर्ती धाराओं के लिए भिन्न होता है।

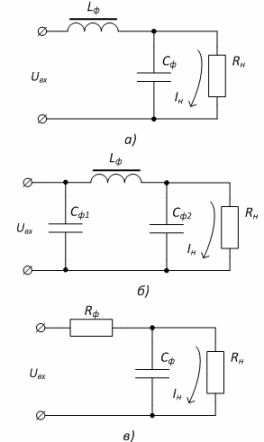

फ़िल्टर तत्व के प्रकार के आधार पर, कैपेसिटिव, इंडक्टिव और इलेक्ट्रॉनिक फ़िल्टर के बीच अंतर किया जाता है। फ़िल्टरिंग लिंक की संख्या के अनुसार, फ़िल्टर को सिंगल-लिंक और मल्टी-लिंक में विभाजित किया गया है।

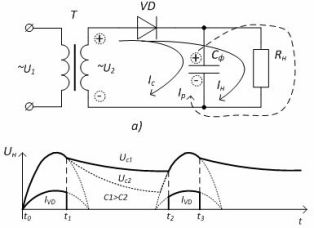

एक कैपेसिटिव फिल्टर एक बड़ी क्षमता वाला कैपेसिटर होता है जो लोड रेसिस्टर Rn के साथ समानांतर में जुड़ा होता है। एक संधारित्र में उच्च डीसी प्रतिरोध और कम एसी प्रतिरोध होता है। आइए आधे-लहर सुधारक सर्किट (चित्र 1, ए) के उदाहरण पर फ़िल्टर के संचालन पर विचार करें।

चित्रा 1-कैपेसिटिव फिल्टर के साथ सिंगल-फेज हाफ-वेव रेक्टिफायर: ए) सर्किट बी) ऑपरेशन के समय आरेख

जब समय अंतराल t0 - t1 (चित्र। 2.63, b) में एक सकारात्मक अर्ध-तरंग बहती है, तो लोड करंट (डायोड करंट) और कैपेसिटर चार्ज करंट प्रवाह।संधारित्र को चार्ज किया जाता है और समय पर t1 संधारित्र में वोल्टेज द्वितीयक वाइंडिंग के वोल्टेज ड्रॉप से अधिक हो जाता है - डायोड बंद हो जाता है और समय अंतराल में t1 - t2 संधारित्र के निर्वहन द्वारा लोड में वर्तमान प्रदान किया जाता है। चे। लोड में करंट लगातार प्रवाहित होता है, जो सुधारित वोल्टेज के तरंग को काफी कम कर देता है।

कैपेसिटर Cf की समाई जितनी बड़ी होगी, उत्तेजना उतनी ही कम होगी। यह संधारित्र के निर्वहन समय द्वारा निर्धारित किया जाता है - निर्वहन समय स्थिर τ = СfRн। τ> 10 पर, चौरसाई गुणांक सूत्र q = 2π fc m Cf Rn द्वारा निर्धारित किया जाता है, जहाँ fc नेटवर्क की आवृत्ति है, m सुधारित वोल्टेज की आधी-अवधि की संख्या है।

कम लोड शक्तियों पर उच्च प्रतिरोध आरएच लोड रोकनेवाला के साथ एक कैपेसिटिव फिल्टर का उपयोग करने की सिफारिश की जाती है।

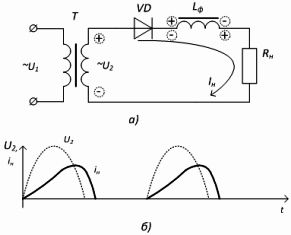

आगमनात्मक फिल्टर (चोक) आरएन (चित्र 3, ए) के साथ श्रृंखला में जुड़ा हुआ है। अधिष्ठापन में कम डीसी प्रतिरोध और उच्च एसी प्रतिरोध होता है। रिपल स्मूथिंग स्व-प्रेरण की घटना पर आधारित है, जो शुरू में करंट को बढ़ने से रोकता है, और फिर इसे कम करने में मदद करता है (चित्र 2, बी)।

चित्रा 2-सिंगल-फेज हाफ-वेव रेक्टीफायर इंडक्टिव फिल्टर के साथ: ए) सर्किट, बी) ऑपरेशन के समय आरेख

आगमनात्मक फिल्टर का उपयोग मध्यम और उच्च शक्ति के रेक्टिफायर में किया जाता है, अर्थात बड़े भार धाराओं के साथ चलने वाले रेक्टिफायर में।

चौरसाई गुणांक सूत्र द्वारा निर्धारित किया जाता है: q = 2π fs m Lf / Rn

कैपेसिटिव और इंडक्टिव फिल्टर का संचालन इस तथ्य पर आधारित है कि नेटवर्क द्वारा खपत करंट के प्रवाह के दौरान, कैपेसिटर और इंडक्टर स्टोर एनर्जी, और जब नेटवर्क से कोई करंट नहीं होता है, या यह घटता है, तो तत्व देते हैं लोड में करंट (वोल्टेज) को बनाए रखते हुए संग्रहीत ऊर्जा का शटडाउन।

मल्टी-जंक्शन फिल्टर कैपेसिटर और इंडिकेटर्स दोनों के स्मूथिंग गुणों का उपयोग करते हैं। कम-शक्ति वाले रेक्टिफायर में, जहाँ लोड रेसिस्टर का प्रतिरोध कई kOhm होता है, चोक Lf के बजाय, रेसिस्टर Rf शामिल होता है, जो फ़िल्टर के द्रव्यमान और आयामों को काफी कम कर देता है।

चित्रा 3 एलसी और आरसी सीढ़ी फिल्टर के प्रकार दिखाता है।

चित्रा 3-मल्टी-जंक्शन फिल्टर: ए) एल-आकार का एलसी, बी) यू-आकार का एलसी, सी) आरसी-फिल्टर

स्टेबलाइजर्स को मुख्य वोल्टेज में उतार-चढ़ाव के दौरान लोड के निरंतर वोल्टेज (वर्तमान) को स्थिर करने के लिए डिज़ाइन किया गया है और लोड द्वारा खपत वर्तमान में परिवर्तन।

स्टेबलाइजर्स को वोल्टेज और करंट स्टेबलाइजर्स के साथ-साथ पैरामीट्रिक और मुआवजे वाले में विभाजित किया गया है। आउटपुट वोल्टेज की स्थिरता का मूल्यांकन स्थिरीकरण कारक Kst द्वारा किया जाता है।

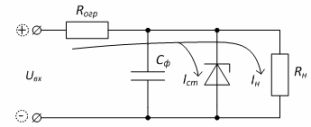

एक गैर-रैखिक विशेषता वाले तत्व के उपयोग के आधार पर पैरामीट्रिक स्टेबलाइजर - एक अर्धचालक जेनर डायोड डिवाइस के माध्यम से रिवर्स वर्तमान में एक महत्वपूर्ण बदलाव के साथ जेनर डायोड का वोल्टेज लगभग स्थिर है।

पैरामीट्रिक स्टेबलाइजर सर्किट को चित्र 4 में दिखाया गया है। इनपुट वोल्टेज UBX को लिमिटिंग रेसिस्टर Rlim और समानांतर-जुड़े जेनर डायोड VD और लोड रेसिस्टर Rn के बीच वितरित किया जाता है।

चित्रा 4 - पैरामीट्रिक स्टेबलाइजर

जैसे-जैसे इनपुट वोल्टेज बढ़ता है, जेनर डायोड के माध्यम से करंट बढ़ेगा, जिसका अर्थ है कि लिमिटिंग रेसिस्टर के माध्यम से करंट बढ़ेगा और इसके आर-पार एक बड़ा वोल्टेज ड्रॉप होगा, और लोड वोल्टेज अपरिवर्तित रहेगा।

पैरामीट्रिक स्टेबलाइज़र में 20-50 के क्रम का Kst होता है। इस प्रकार के स्टेबलाइजर्स के नुकसान कम स्थिरीकरण धाराएं और कम दक्षता हैं।

पैरामीट्रिक स्टेबलाइजर्स का उपयोग सहायक वोल्टेज स्रोतों के रूप में किया जाता है, साथ ही जब लोड करंट छोटा होता है - सैकड़ों मिलीमीटर से अधिक नहीं।

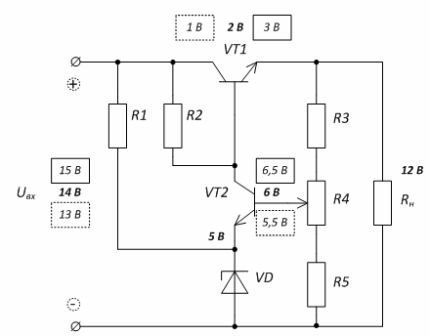

एक प्रतिपूरक स्टेबलाइज़र ट्रांजिस्टर के चर प्रतिरोध को एक सीमित अवरोधक के रूप में उपयोग करता है। जैसे-जैसे इनपुट वोल्टेज बढ़ता है, ट्रांजिस्टर का प्रतिरोध भी बढ़ता है, तदनुसार, जैसे-जैसे वोल्टेज घटता है, प्रतिरोध घटता जाता है। इस स्थिति में, लोड में वोल्टेज अपरिवर्तित रहता है।

ट्रांजिस्टर का स्टेबलाइजर सर्किट चित्र 5 में दिखाया गया है। आउटपुट वोल्टेज यूआरएन के नियमन का सिद्धांत विनियमन ट्रांजिस्टर वीटी1 की चालकता में बदलाव पर आधारित है।

चित्रा 5 - क्षतिपूर्ति वोल्टेज नियामक की योजनाबद्ध

एक वोल्टेज तुलना सर्किट और एक डीसी एम्पलीफायर ट्रांजिस्टर VT2 पर इकट्ठे होते हैं। मापने वाला सर्किट R3, R4, R5 इसके बेस सर्किट में शामिल है, और संदर्भ वोल्टेज स्रोत R1VD एमिटर सर्किट में शामिल है।

उदाहरण के लिए, जैसे-जैसे इनपुट वोल्टेज बढ़ता है, आउटपुट भी बढ़ेगा, जिससे ट्रांजिस्टर VT2 के आधार पर वोल्टेज में वृद्धि होगी, जबकि उसी समय एमिटर VT2 की क्षमता समान रहेगी।इससे बेस करंट में वृद्धि होगी, और इसलिए ट्रांजिस्टर VT2 का कलेक्टर करंट - ट्रांजिस्टर VT1 की बेस क्षमता कम हो जाएगी, ट्रांजिस्टर बंद हो जाएगा और उस पर एक बड़ा वोल्टेज ड्रॉप होगा, और आउटपुट वोल्टेज होगा अपरिवर्तित ही रहेंगे।

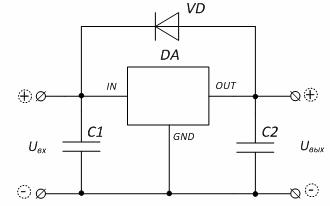

आज स्टेबलाइजर्स का उत्पादन एकीकृत परिपथों के रूप में किया जाता है। एक एकीकृत स्टेबलाइजर को चालू करने की एक विशिष्ट योजना चित्र 6 में दिखाई गई है।

चित्रा 6 - अंतर्निर्मित वोल्टेज स्टेबलाइज़र चालू करने के लिए विशिष्ट योजनाबद्ध

स्टेबलाइजर माइक्रोक्रिकिट के आउटपुट का पदनाम: "इन" - इनपुट, "आउट" - आउटपुट, "जीएनडी" - सामान्य (केस)। यदि स्टेबलाइजर समायोज्य है, तो आउटपुट "एडीजे" - समायोजन है।

स्टेबलाइज़र का चयन आउटपुट वोल्टेज के मान, अधिकतम लोड करंट और इनपुट वोल्टेज की भिन्नता की सीमा पर आधारित होता है।